- 您现在的位置:买卖IC网 > Sheet目录1889 > AD5200BRMZ50-REEL7 (Analog Devices Inc)IC POT DGTL 50K 256POS 10MSOP

AD5200/AD5201

–14–

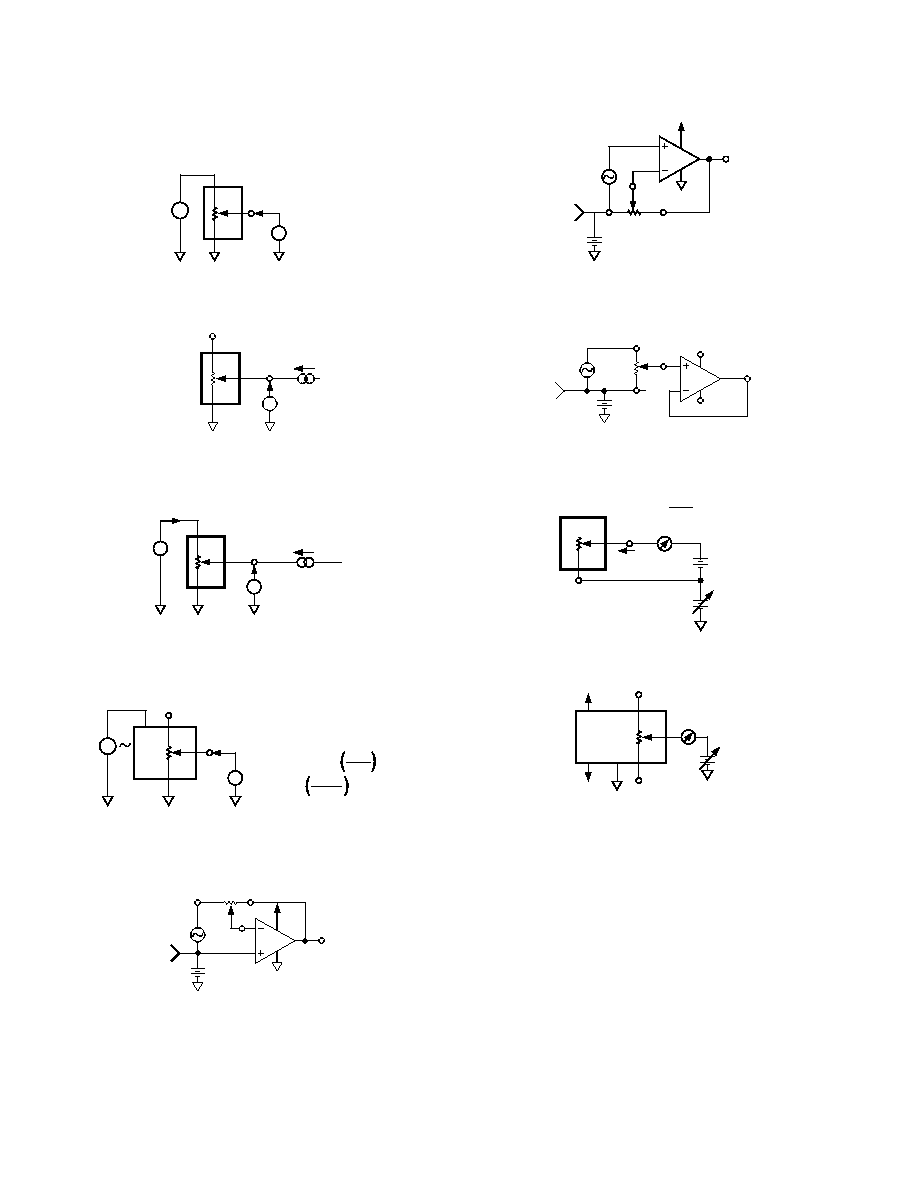

TEST CIRCUITS

Figures 6 to 14 define the test conditions used in the product

specification table.

VMS

A

W

B

DUT

V+

V+ = VDD

1 LSB = V+/2N

Figure 6. Potentiometer Divider Nonlinearity Error Test

Circuit (INL, DNL)

VMS

A

W

B

DUT

NO CONNECT

IW

Figure 7. Resistor Position Nonlinearity Error

(Rheostat Operation; R-INL, R-DNL)

VMS1

A

W

B

DUT

IW = VDD/RNOMINAL

VMS2

VW

RW = [VMS1 – VMS2]/IW

Figure 8. Wiper Resistance Test Circuit

VMS%

VDD%

PSS (%/%) =

V+ = VDD 10%

PSRR (dB) = 20 LOG

VMS

VDD

VMS

A

W

B

V+

VDD

VA

Figure 9. Power Supply Sensitivity Test Circuit

(PSS, PSRR)

OP279

W

5V

B

VOUT

OFFSET

GND

OFFSET BIAS

A

DUT

VIN

Figure 10. Inverting Gain Test Circuit

OFFSET BIAS

B

OFFSET

GND

A

DUT

OP279

W

5V

VOUT

VIN

Figure 11. Noninverting Gain Test Circuit

OP42

VOUT

VIN

+15V

OFFSET

GND

–15V

W

B

A

2.5V

Figure 12. Gain vs. Frequency Test Circuit

W

B

VSS TO VDD

DUT

ISW

CODE = OOH

RSW =

0.1V

ISW

0.1V

+

–

Figure 13. Incremental ON Resistance Test Circuit

ICM

A

W

B

NC

GND

NC

VSS

VDD

DUT

VCM

NC = NO CONNECT

Figure 14. Common-Mode Leakage Current Test Circuit

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

AD5203ARZ100

IC POT DGTL QUAD 64POS 24SOIC

AD5204BRZ50

IC DGTL POT QUAD 50K 24-SOIC

AD5207BRU50

IC DGTL POT DUAL 256POS 14TSSOP

AD5220BNZ50

IC POT DGTL SGL 128POS 8DIP

AD5222BRUZ100

IC POT DGTL DUAL 128POS 14TSSOP

AD5227BUJZ10-R2

IC DGTL POT 10K UP/DN TSOT23-8

AD5228BUJZ50-R2

IC DGTL POT 50K UP/DN TSOT23-8

AD5231BRU50-REEL7

IC DGTL POT 1024POS 16-TSSOP TR

相关代理商/技术参数

AD5201

制造商:AD 制造商全称:Analog Devices 功能描述:256-Position and 33-Position Digital Potentiometers

AD5201BD

制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Analog Devices 功能描述:

AD5201BRM10-REEL7

制造商:Rochester Electronics LLC 功能描述:5-BIT DIGITAL POT - Tape and Reel 制造商:Analog Devices 功能描述:

AD5201BRM50

制造商:Analog Devices 功能描述:Digital Potentiometer 33POS 50KOhm Single 10-Pin MSOP 制造商:Rochester Electronics LLC 功能描述:5-BIT DIGITAL POT - Bulk

AD5201BRM50-REEL7

制造商:Analog Devices 功能描述:Digital Potentiometer 33POS 50KOhm Single 10-Pin MSOP T/R 制造商:Rochester Electronics LLC 功能描述:5-BIT DIGITAL POT - Tape and Reel

AD5201BRMZ10

功能描述:IC DGTL POT 10K 33POS 10-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数字电位器 系列:- 标准包装:3,300 系列:WiperLock™ 接片:257 电阻(欧姆):100k 电路数:1 温度系数:标准值 150 ppm/°C 存储器类型:易失 接口:3 线 SPI(芯片选择) 电源电压:1.8 V ~ 5.5 V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-VDFN 裸露焊盘 供应商设备封装:8-DFN-EP(3x3) 包装:带卷 (TR)

AD5201BRMZ10-REEL7

功能描述:IC DGTL POT 10K 33POS 10-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数字电位器 系列:- 标准包装:3,000 系列:DPP 接片:32 电阻(欧姆):10k 电路数:1 温度系数:标准值 300 ppm/°C 存储器类型:非易失 接口:3 线串行(芯片选择,递增,增/减) 电源电压:2.5 V ~ 6 V 工作温度:-40°C ~ 85°C 安装类型:表面贴装 封装/外壳:8-WFDFN 裸露焊盘 供应商设备封装:8-TDFN(2x3) 包装:带卷 (TR)

AD5201BRMZ50

功能描述:IC DGTL POT 50K 33POS 10-MSOP RoHS:是 类别:集成电路 (IC) >> 数据采集 - 数字电位器 系列:- 标准包装:3,300 系列:WiperLock™ 接片:257 电阻(欧姆):100k 电路数:1 温度系数:标准值 150 ppm/°C 存储器类型:易失 接口:3 线 SPI(芯片选择) 电源电压:1.8 V ~ 5.5 V 工作温度:-40°C ~ 125°C 安装类型:表面贴装 封装/外壳:8-VDFN 裸露焊盘 供应商设备封装:8-DFN-EP(3x3) 包装:带卷 (TR)